# Образовательные технологии проектирования цифровых систем на кристаллах в учебном процессе ХНУРЭ

#### **Vladimir Hahanov**

Dean of Computer Engineering Faculty,

Doctor of Science, Professor,

IEEE Computer Society Golden Core Member

## Agenda

- Education in Kharkov

- University Faculties

- Companies our partners for education and working

- Our projects

- Club's Education

- East-West Design & Test Symposium 2007

- Educational projects

- What we are waiting from IT-industry and Cadence

#### **Kharkov**

- Population: 1.5 millions

- Science and education center

- 60 research institutes

- 30 higher education institutes

- 80 libraries

- 655.1 thousands of pupils, including 280000 students

- 3915 PhD students

- 1700 doctors of science

- Students from 90 countries

- 160 specialties

- 12 of 73 objects, which are national patrimony of Ukraine, are located in Kharkov

- Kharkov is scientific and educational leader of Ukraine.

- Unemployed: 44.3 thousands people

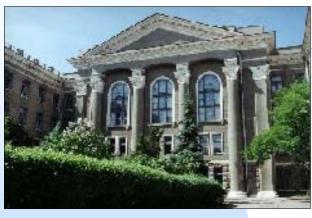

## Kharkov National University of Radio Electronics

- Kharkov National University of Radio Electronics was founded 75 years ago.

- It was one of the best University in USSR in 70th 90th in the field of Radio electronics. Today the University is the leader among all technical universities of Ukraine.

- Total number of students is more than 12000, 150 professors and doctors of science.

- 500 PhD and professor assistants work in the University.

- Technical equipment of laboratories is more than 1200 computers. The students of our University acquire professions which are required not only in Ukraine but in other countries also.

- Graduate students of our University work in USA, Germany, England, Finland, France, Poland as well.

- The University consists of 7 faculties. The faculty of Computer Engineering and Control is one of the best not only in the university but among other technical universities, which have similar specialties.

#### World leading companies manage Computer **Engineering Faculty**

### History of brands contacts

IEEE **Microsoft** IT Academy Program KW(LITA(KOLO COMPUTER 2006 SYNOPSYS° 2005 Microsoft<sup>®</sup> 2004 'intel' freescale<sup>\*</sup> 2003 2002 2001 cādence 2000 1999 **Free**Code 1998 Design Verification Company

### **Faculties in KNURE**

- FACULTY OF COMPUTER ENGINEERING AND CONTROL Dean Prof. Hahanov Vladimir Ivanovich (1654 students)

- Faculty of Computer Sciences Dean Prof. Mashtalir Vladimir Petrovich (1651 students)

- Faculty of Applied Mathematics and Management Dean Prof. Doroshenko Volodymyr Oleksiyovich (822 students)

- Faculty of Radio Engineering Dean Prof. Sakalo Serguei Nikolaevich (675 students)

- Faculty of Telecommunication Systems Dean Prof. Popovsky V.V. (986 students)

- Faculty of electronic devices Dean Prof. Filipenko Alexander Ivanovich (775 students)

- Faculty of electronic engneering Dean Prof. Alexandrov Yuri Nikolaevich (558 students)

## **Computer Engineering Faculty**

Number of students: 1654;

Number of employees: 154 сотрудника;

Number of teachers 120 (77 PhDs, 15 Dr of Sciences);

6 laboratories and more than 300 PC stations,

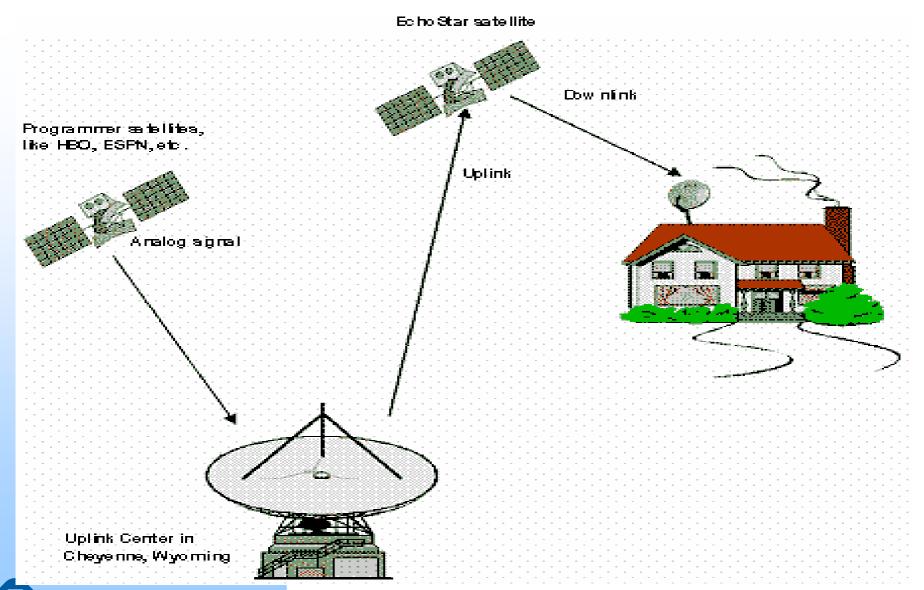

**6 offices from local and brand industries -** Aldec, Kaspersky Lab, Freecode, Softline, Institute of Information Technology, ADB, Echostar is coming.

More than 300 foreign students from 12 countries studying in English.

#### **Departments:**

- CAD Department 21 employees (Specialized Computer Systems),

- Computer Systems Department 65 employees (Computer Systems and Networks, System, Programming),

- Information Technology Security 26 employees (Information Security in Computer Systems and Networks).

#### Others specialties:

- Control Systems and Automation

- Flexible Computer Systems in Robotics

- Wireless Computer Systems and Networks

### **KNURE** rate for today

KNURE is the first University in Ukraine in area of Radio Electronics.

KNURE is the 31st University in Ukraine among 200 Universities.

According to Ukraine Universities rate, Kharkov National University of Radio Electronics has 6 rank from list of Technical Universities (total number is 30):

**Kiev Polytechnic University**

- Kharkov Polytechnic University

- Kharkov Aerospace University 59 Raitio

- Asov Technical University

- Lviv Polytechnic University

- Kharkov National University of RadioElectronics

### 50 Universities – Partners of CAD-dept.

**Yerevan University**

Saratov State

University

Nizhny Novgorod

University

Tallinn University of Technology

**Purdue University**

of Technology

**Warsaw University**

Rennes University

**Sophia University**

Turino University of Technology

Dresden University of Technology

**Las Vegas University**

**Bialystok University**

Bielorussia University of RadioTechnics

#### 30 Ukrainian Universities - Partners of CAD-dept.

### Special HW/SW courses in KNURE

- CE039 Computer electronics 4 ECTS

- CE001 Computer circuit design 6 ECTS

- CE002 Computer architectures 6 ECTS

- CE003 System programming 6 ECTS

- CE005 System software 6 ECTS

- CE015 Specialized microprocessor systems design 4 ECTS

- CE044 Computer systems and networks information security 3 ECTS

- CE008 Logic simulation 4 ECTS

- CE011 PLD Design Automation Methods 4,5 ECTS

- CE002 OBJECT-ORIENTED PROGRAMMING 3 ECTS

- CE007 HARDWARE DESCRIPTION LANGUAGES 3 ECTS

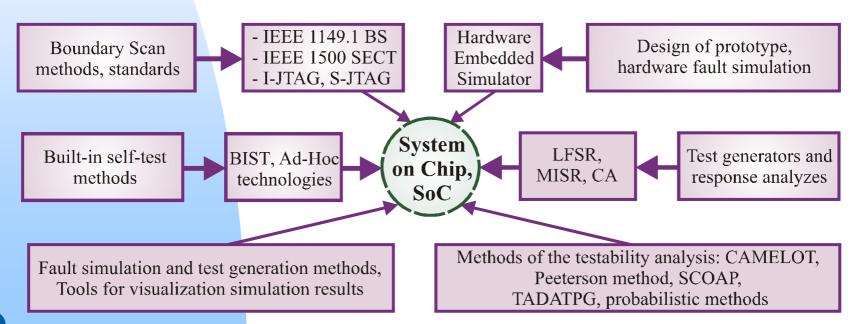

- CE012 BASIS OF COMPUTER DIAGNOSTICS

- CE013 SPECIALIZED COMPUTER SYSTEM ARCHITECTURES

- CE014 MICROPROCESSOR TECHNOLOGY (SPECIALISED COMPUTER SYSTEMS)

- CE005 OPERATING SYSTEM

- CE006 TEXT AND GRAPHIC EDITORS (Specialized Computer Systems)

- CE002 OBJECT-ORIENTED PROGRAMMING 3 ECTS

- CE041 PARALLEL AND DISTRIBUTED COMPUTING 3 ECTS

- CE042 COMPUTER SYSTEMS 5 ECTS

- CE043 COMPUTER NETWORKS 5 ECTS

- CE004 COMPUTER SYSTEMS DESIGN AUTOMATION 3 ECTS

- CS002 DATABASE ORGANIZATION AND DATA PROCESSING 3 ECTS

#### HW/SW RF and TV courses in KNURE

- HW/SW Design and Testing

- Design Automation, 156 hours

- HDL Languages (VHDL, Verilog, System C), 156 hours

- SW languages (C++, C#, Jawa, .Net), 156 hours

- Technology and CAD Tools, 108 hours

- Digital Systems Testing and Testable Design, 156 hours

- RF/Analog design

- Computer Aided A/RF-Design, 162 hours

- Computer RF/A simulation, 162 hours

- Digital TV

- Television standards and record formats, 216 hours

- Digital recording and playback devices, 108 hours

- DSP, 108 hours

## Conferences, organized by KNURE

- ☐ IEEE East- West Design & Test Conference

- ☐ International Workshop "Information technologies to Science and Education"

- Microsoft Academic Days

- □ Kaspersky Workshop

- International Radioelectronics Forum

- ☐ International Youth Conference "Radio Electronics and Youth in the XXI Century"

- Education and Virtuality

- ☐ International Conference on physics of Laser Crystals

- ☐ International Conference on Precision Oscillations

- ☐ International Conference on Navigation and Location systems

- International Conference on Telecommunication technologies and Networks

- International Conference on Information systems and Technologies

- ☐ International Conference on Optoelectronics

- International Conference on Microelectronics and Nanotechnology

- ☐ International Conference on Electromagnetic Compatibility and Survivability

## «Intel Technologies School of Multicore»

3-12 мая 2007 года

- Харьковский Национальный Университет радиоэлектроники

- Проводится по инициативе и при поддержке компании Intel совместно с университетами Харькова, Нижнего Новгорода, Ростова-на-Дону, Таганрога

- Программа Technologies School of Multicore:

- 1) Apхитектура Intel Core 2 Duo;Intel tools: Compiler, VTune, MKL, IPP, Thread checker, Thread Profiler;Программирование PThreads, OpenMP;Масштабируемость многопоточных приложений.

- Темы тренинга: Введение в высокопроизводительные вычисления, средства программирования для параллельных вычислительных систем, параллельные алгоритмы в моделировании физических явлений и визуализации данных в реальном масштабе времени, система МС# как язык для многопоточного программирования на мультиядерных процессорах, технологии параллельного программирования, мастер-класс по Grid-технологиям. Занятия проводятся сотрудниками компании Intel и участниками конкурса Intel по обновлению учебнометодических материалов, посвященных программированию на многоядерных архитектурах.

- Организационный комитет: Нижний Новгород: (8312) 16-24-91,

- Фадина Лариса Михайловна,

- Харьков: (8057) 70-21-326, Хаханов Владимир Иванович

#### Awards of students.1

- ☐ IEEE Recognition Award

- ☐ IEEE Gerald W. Gordon Award

- □ Diploma for Best Scientific Project in CAD Projects contest by Intel 2003

- Diploma of Ukrainian Ministry of Science and Education for the Best Systems Program

- Diploma of Ukrainian Ministry of Science and Education in nomination "For professionalism"

- Diploma for the Best Student's Application

- Diploma for "Mobile Games Development Kit" in J2ME contest by Sun Microsystems

- □ 14 Diplomas for student Olympiads

#### Awards of students.2

- ☐ Diploma of the 1<sup>st</sup> place winner in Ukrainian Olympiad on Digital Systems Testing, 2006

- □ Diploma of the 3<sup>rd</sup> place winner in Microsoft Imagine Cup, 2006

- □ Diploma of the best scientist nomination in Concourse of Kharkov Citizen, 2006

- □ Diploma of IEEE Computer Society Golden Core Member, 2006

- **☐** EWDT Sponsorship by Microsoft, 2006

- EWDT Sponsorship by Intel, 2006

- ☐ EWDT Sponsorship by Cadence, 2006

### Scientific results of CAD department

- □ 86 published papers including 5 in foreign journals; 49 – conferences out of USSR, 2006

- 14 students and professors are attended in international fairs, 2006

- □ 32 international program and grants, 2005

- □ 24 Diplomas in area of IT-science and technology, 2005, 2006

- □ 12 TV air translation devoted achievement of our team, 2006, 2 TV for the current Year

- ☐ 7 dissertations including Doctor of Science prepared for defense in 2007

### **Projects**

- SIGETEST- fault simulation and test generation for complex digital devices

- PRUS programmable unlimited systems, spherical multiprocessor for Boolean equations solving

- □ Independent Test Lab:

- INFOWATCH Mail Storage

- Kaspersky Antivirus

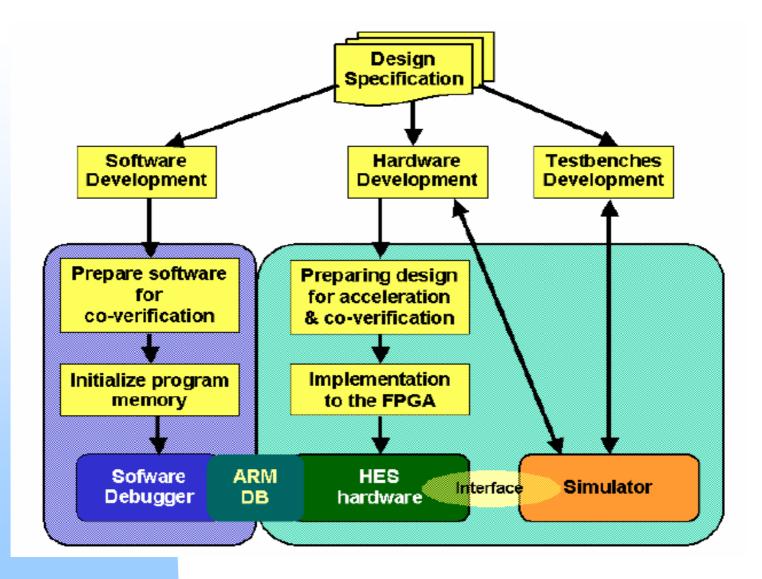

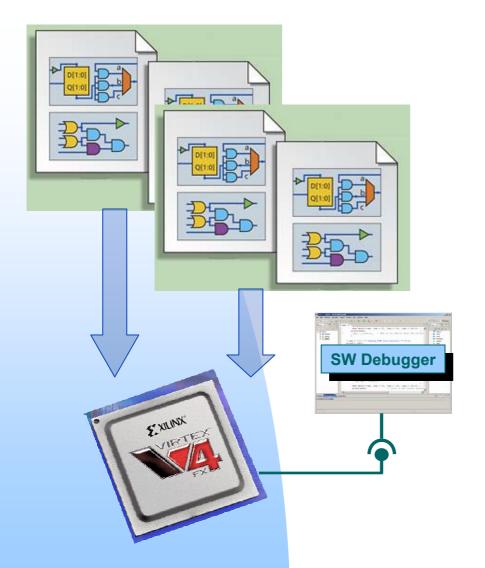

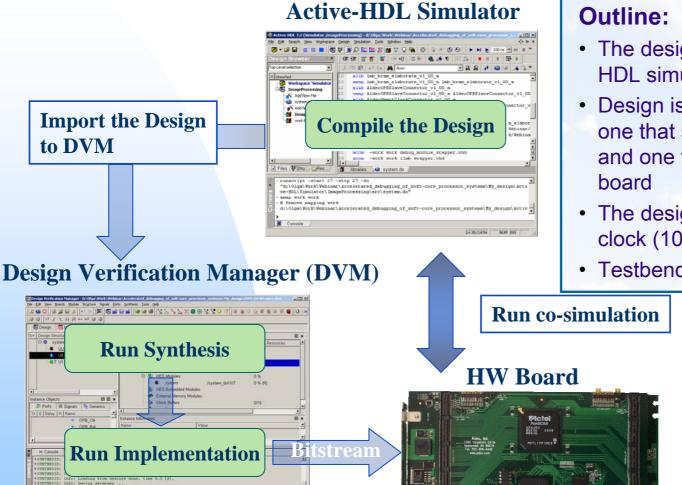

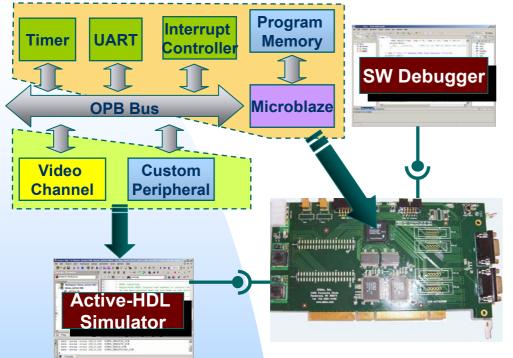

- HES+ARM Board HW/SW co-simulator for complex SoCs verification

- Assertions Engine temporal assertions checker

- □ CORDIC IP Core generator for fast calculations of trigonometric functions in hardware

- JPEG/MPEG4 SoC implementation (R&D)

- OpenTEST Knowledge testing computer system

- ASFTEST automatic test synthesis system for state machines

- eXCite Tool Testing

- LAN Analyzer based on Novell ZEN MS, Norway

#### LINT – СИСТЕМА ДИАГНОСТИРОВАНИЯ HDL-ПРОЕКТОВ

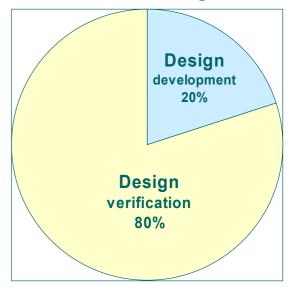

- Мотивация определяется тремя основными проблемами при разработке аппаратуры: 1) Высокая стоимость (до 1000000 долларов) исправления ошибок на поздних стадиях проектирования цифровых систем; 2) Менеджмент и координация командной разработки сверхсложных проектов; 3) Уменьшение интервала времени для выхода готового продукта на рынок электронных технологий.

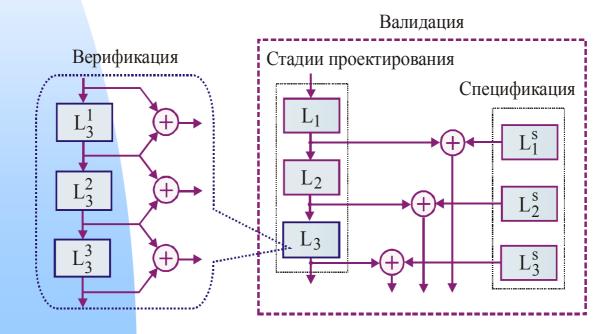

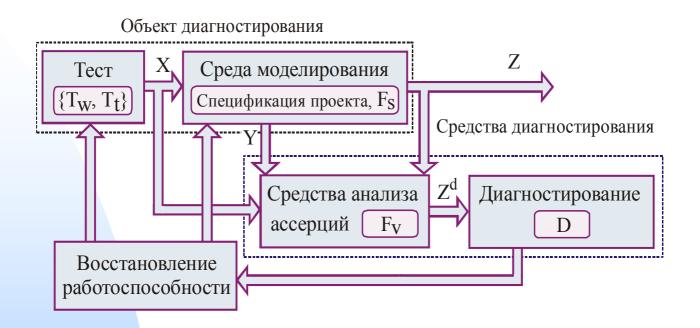

- Цель предложенной разработки минимизация материальных затрат и времени проектирования сверхсложных (более 1 000 000 вентилей) цифровых систем на кристаллах за счет использования программного комплекса автоматизированного диагностирования функциональных неисправностей на ранних стадиях проектирования. Отличительная особенность используется lint-технология, реализующая библиотеку стандартных и оптимальных решений от мировых производителей SoC в процессе создания кода, инвариантного к стандартам и маршрутам проектирования ведущих EDA-компаний мира.

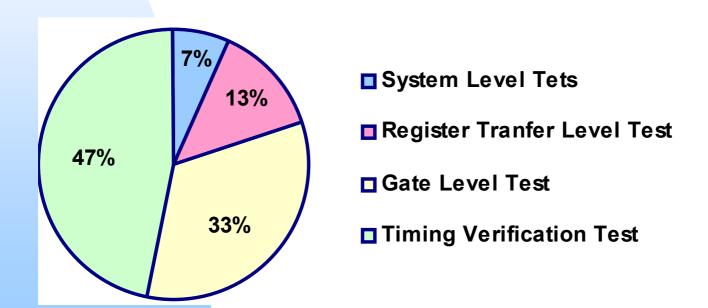

- Функциональности LINT- системы диагностирования: 1) Сканирование исходного HDL-кода для создания внутренней модели проекта; 2) Анализ модели в целях диагностирования функциональных (семантических) несоответствий относительно заданных правил и шаблонов; 3) Верификация валидной синтезируемости конструкций RTL-модели в целях обеспечения ее полного соответствия с пост-синтезной моделью вентильного уровня; 4) Поддержка IEEE-стандартов тестопригодного проектирования; 5) Семантическая проверка test bench, как кода, дополняющего проект.

- Научная новизна впервые предложена универсальная модель диагностирования функциональных неисправностей на ранних стадиях проектирования и модель поиска шаблонов диагностирования сложных правил проектирования, не проверяемых конкурентами.

- Рыночная привлекательность: 10000 инсталляций в США, Азии, Европе. LINT-система диагностирования работает под управлением ОС Windows, LINUX/UNIX, SUN. Конкуренты (Synopsis LEDA, Atrenta Spyglass, TransEDA Vn-Check) имеют аналогичные средства, ориентированные только для ОС LINUX и SUN.

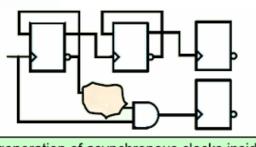

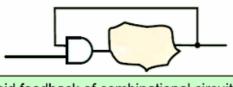

## Riviera LINT: fresh approach to RTL design rules checking

Avoid generation of asynchronous clocks inside a circuit

Avoid feedback of combinational circuits

Avoid feedback that spans asynchronous reset

#### Patterns recognition on synthesized netlist:

- combinational loops

- mixing feedbacks and asynchronous controls

- clock tree / initial reset tree distribution

- Design-For-Test constraints

- gated clocks

#### Powerful configurability features:

- Configuration files with settings

- Rulesets / Policies

- Parameterization of existing rules

- Embedded pragmas for in-place errors masking

- C++ API for custom user-defined rules

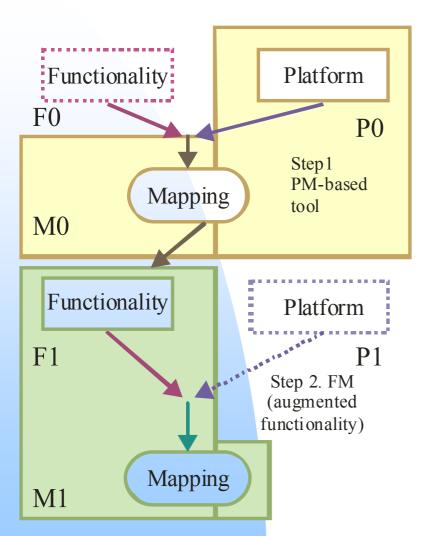

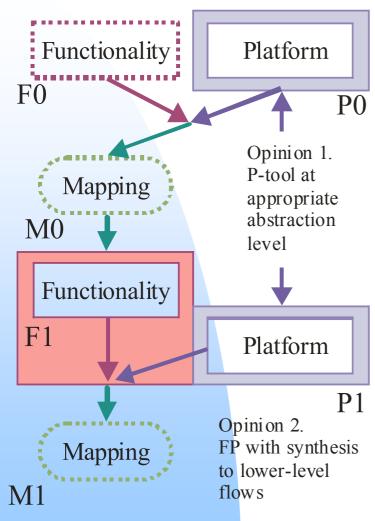

## **Design Flow**

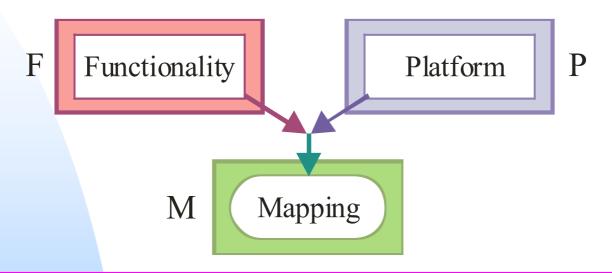

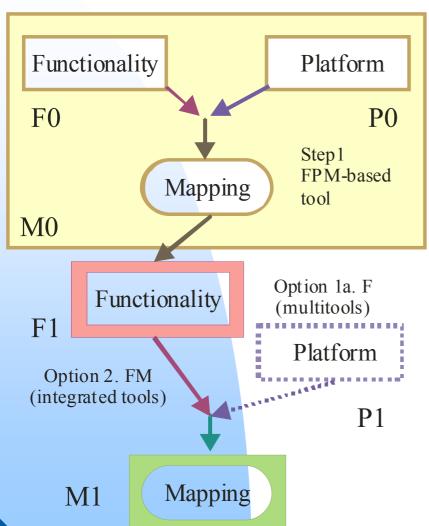

## Electronic system-level design tools. Platform-based design classification framework elements

- Functionality indicates functional representations of a design completely independent of implementations architecture.

- Platform concerns the modules used to implement the functional description for example, processors, memories, and custom hardware.

- Mapping refers to instances of the design in which the functionality has been assigned to a set of correctly interconnected modules.

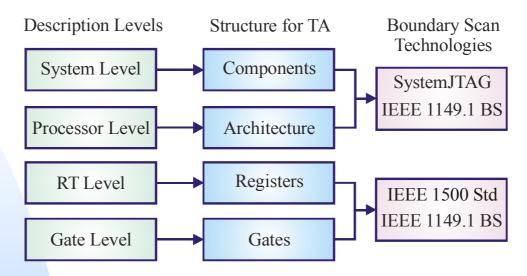

#### **Abstraction levels**

- <u>System level S</u> correspond to heterogeneous designs that use different models of computation (MoCs) to represent function, platform, and mappings.

- <u>Component level C</u> involves subsystems containing homogeneous components.

- Implementation level I comprises the final design step, when the design team considers the job complete.

## Scenario 1: New application design from specification

The requirements of this scenario include the need to start from highlevel specification; the desire to capture and modify the initial specification quickly, the ability to express concurrency, constraints and other behavior-specific characteristics efficiently; and the ability to capture useful abstract services for implementing high-level specifications into a more detailed functional view.

## Scenario 2: New integration platform development

This scenario describes the development of a new integration platform: a hardware architecture, embedded-software architecture, design methodologies (authoring and integration), design guidelines and modeling standards, virtualcomponents characterization and support, and design verification, focusing on a particular target application.

#### Scenario 3 Legacy design integration

The scenario represents a common situation for many companies wishing to integrate their existing designs into new ESL flows

| Table 1. Tools in bin F: Industrial.(C: component level; I: Implementation level; S:system level |                                            |                     |                           |  |  |

|--------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------|---------------------------|--|--|

| Tools                                                                                            | Focus                                      | Abstraction         | Web site                  |  |  |

|                                                                                                  | High-level technical computing language    |                     |                           |  |  |

|                                                                                                  | and interactive environment for algorithm  | S: Matlab language, |                           |  |  |

|                                                                                                  | development, data visualization, analysis, | vector, and matrix  | http://www.mathworks.com  |  |  |

| Matlab                                                                                           | and numerics computation                   | operations          | /products/matlab          |  |  |

|                                                                                                  | Graphically model, compile, and simulate   |                     |                           |  |  |

| Scicos                                                                                           | dynamic systems                            | S: Hybrid systems   | http://www.scilab.org     |  |  |

| Verdi                                                                                            | Debugging for System Verilog               | I: Discrete event   | http://www.novas.com      |  |  |

|                                                                                                  |                                            | S:VHDL-AMS,         | http://www.mentor.com/pro |  |  |

| SystemVision                                                                                     | Mixed-signal and high-level simulation     | Spice, C            | ducts/sm/systemvision     |  |  |

|                                                                                                  | Military and aerospace system-level        | S: Performance      |                           |  |  |

| EDAStar                                                                                          | design                                     | models              | http://www.edaptive.com   |  |  |

| DBRover,                                                                                         |                                            |                     |                           |  |  |

| TemporalRover,                                                                                   | Temporal rules checking, pattern           | C: Statecharts      |                           |  |  |

| StateRover                                                                                       | recording, and knowledge reasoning         | assertions          | http://www.time-rover.com |  |  |

|                                                                                                  | Mathematical problem devolopment and       | S: Mathematical     |                           |  |  |

| Maple                                                                                            | solving                                    | equations           | http://www.maplesoft.com  |  |  |

|                                                                                                  | Graphical mathematical development and     |                     |                           |  |  |

|                                                                                                  | problem solving with support for Java, C,  | S: Mathematical     |                           |  |  |

| Mathematica                                                                                      | and Net                                    | equations           | http://www.wolfram.com    |  |  |

|                                                                                                  | Process-oriented, general-purpose          |                     |                           |  |  |

| CSIM 19                                                                                          | simulation toolkit for C and C++           | S: C. C++           | http://www.mesquite.com   |  |  |

|                                                                                                  |                                            | C: Timed            |                           |  |  |

|                                                                                                  |                                            | synchronous         |                           |  |  |

| Agilent Ptolemy                                                                                  | Functional verification                    | dataflow            | http://www.agilent.com    |  |  |

|                                                                                                  |                                            | S: LabView          |                           |  |  |

|                                                                                                  | Test, measurement, and control             | programming         |                           |  |  |

| LabView                                                                                          | application development                    | language            | http://www.ni.com/labview |  |  |

Table. Tools in bin P: Industrial.

| Solutions to package and deploy IP in a repeatable, Solutions EASI-Studio reliable manner C: Interconnection com  FPGAS, CPLDS, and structured I: IP blocks, C, and Altera Quatrus II ASICs RTL; FPGAS http://www.altera.com  Platform Xilinx Studio IP integration framework C: IP blocks, FPGAS http://www.xilinx.com http://www.mentor.com/pro ducts/embedded software/ graphics Nucleus systems and development tools S: Software nucleus rtos  Sonics On-chip interconnection I: Bus-functional Studio infrastructure models http: sonicsinc.com  ISE, EDK, FPGAS, CPLDS, and structured I: IP blocks, C, and Xilinx XtremeDSP ASICs RTL; FPGAs http://www.xilinx.com  Hosted  Design and Extranet Reuse Services IP delivery systems S: All types of IP reuse.com  Software Configurable Compile a subset of C into Processor hardware for instruction configurable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Provider  | Tools       | Focus                         | Abstraction          | Web site                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|-------------------------------|----------------------|----------------------------|

| Standards-based IP libraries SystemC, VHDL for SoCs http://www.prosilog.com  Solutions to package and deploy IP in a repeatable, Solutions EASI-Studio reliable manner C: Interconnection com  FPGAs, CPLDs, and structured I: IP blocks, C, and RTL; FPGAs http://www.altera.com  Platform  Xilinx Studio IP integration framework C: IP blocks, FPGAs http://www.mentor.com/products/embedded_software/graphics Nucleus systems and development tools S: Software nucleus rtos  Sonics On-chip interconnection I: Bus-functional models http://sonicsinc.com  ISE, EDK, FPGAs, CPLDs, and structured I: IP blocks, C, and RTL; FPGAs http://www.mentor.com/products/embedded_software/nucleus_rtos  Sonics On-chip interconnection I: Bus-functional models http: sonicsinc.com  ISE, EDK, FPGAs, CPLDs, and structured I: IP blocks, C, and RTL; FPGAs http://www.xilinx.com  Hosted Design and Extranet Reuse Services IP delivery systems S: All types of IP reuse.com  Software Configurable Compile a subset of C into C: Software-configurable compiler extensions processors http://www.stretchinc.com  Transaction-based verification C: FPGA-based rapid http://www.prodesign-integrations.com http://www.prodesign-integration http://www.prodesign-integration.com  |           |             |                               | C: RTL and           |                            |

| Prosilog Nepsys and support tools (SystemC) SoCs http://www.prosilog.com  Solutions to package and deploy IP in a repeatable, reliable manner  EASI-Studio reliable manner  C: Interconnection com  FPGAs, CPLDs, and structured I: IP blocks, C, and RTL; FPGAs  Platform  Xilinx Studio IP integration framework  C: IP blocks, FPGAs http://www.altera.com  Pamily of real time operating ducts/embedded software/ nucleus ross  Sonics On-chip interconnection  Sonics Studio infrastructure models http://www.rilinx.com  ISE, EDK, FPGAs, CPLDs, and structured I: IP blocks, C, and  Xilinx XtremeDSP ASICs RTL; FPGAs http://www.xilinx.com  Hosted Design and Extranet  Reuse Services IP delivery systems S: All types of IP reuse.com  Software Configurable Compile a subset of C into Processor hardware for instruction configurable  Stretch compiler extensions processors http://www.prodesign-  Transaction-based verification C: FPGA-based rapid http://www.prodesign-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |             |                               | transaction-level    |                            |

| Solutions to package and deploy IP in a repeatable, Solutions EASI-Studio reliable manner C: Interconnection com  FPGAs, CPLDs, and structured I: IP blocks, C, and AItera Quatrus II ASICs RTL; FPGAs http://www.altera.com  Platform Xilinx Studio IP integration framework C: IP blocks, FPGAs http://www.altera.com  Mentor Family of real time operating systems and development tools S: Software nucleus rtos  Sonics On-chip interconnection I: Bus-functional models http://www.xilinx.com  ISE, EDK, FPGAs, CPLDs, and structured I: IP blocks, C, and XIIInx XtremeDSP ASICs RTL; FPGAs http://www.xilinx.com  Hosted Design and Extranet Reuse Services IP delivery systems S: All types of IP reuse.com  Software Configurable Compile a subset of C into C: Software-processor hardware for instruction configurable compiler extensions processors http://www.prodesign-processors http://www.prodesign-process |           |             | Standards-based IP libraries  | SystemC, VHDL for    |                            |

| Beach Solutions EASI-Studio reliable manner C: Interconnection com  FPGAs, CPLDs, and structured I: IP blocks, C, and Altera Quatrus II ASICs RTL; FPGAs http://www.altera.com  Platform  Xilinx Studio IP integration framework C: IP blocks, FPGAs http://www.altera.com  Mentor Family of real time operating systems and development tools S: Software nucleus rtos  Sonics On-chip interconnection I: Bus-functional infrastructure models http://www.xilinx.com  ISE, EDK, FPGAs, CPLDs, and structured I: IP blocks, C, and Xilinx XtremeDSP ASICs RTL; FPGAs http://www.xilinx.com  Hosted Design and Extranet Reuse Services IP delivery systems S: All types of IP reuse.com  Stretch compiler extensions processors http://www.stretchinc.com  Transaction-based verification C: FPGA-based rapid http://www.prodesign-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Prosilog  | Nepsys      | and support tools (SystemC)   | SoCs                 | http://www.prosilog.com    |

| Solutions EASI-Studio reliable manner C: Interconnection com  FPGAs, CPLDs, and structured I: IP blocks, C, and RTL; FPGAs http://www.altera.com  Platform  Xilinx Studio IP integration framework C: IP blocks, FPGAs http://www.xilinx.com  Mentor Family of real time operating Graphics Nucleus systems and development tools S: Software nucleus rtos  Sonics On-chip interconnection I: Bus-functional models http://sonicsinc.com  ISE, EDK, FPGAs, CPLDs, and structured I: IP blocks, C, and XtremeDSP ASICs RTL; FPGAs http://www.xilinx.com  Wilinx XtremeDSP ASICs RTL; FPGAs http://www.xilinx.com  Hosted Design and Extranet Reuse Services IP delivery systems S: All types of IP reuse.com  Software Configurable Compile a subset of C into Processor hardware for instruction configurable  Stretch compiler extensions processors http://www.stretchinc.com  Transaction-based verification C: FPGA-based rapid http://www.prodesign-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |             | Solutions to package and      |                      |                            |

| FPGAs, CPLDs, and structured I: IP blocks, C, and Altera Quatrus II ASICs RTL; FPGAs http://www.altera.com  Platform Xilinx Studio IP integration framework C: IP blocks, FPGAs http://www.xilinx.com  Mentor Family of real time operating systems and development tools S: Software nucleus rtos  Sonics On-chip interconnection I: Bus-functional infrastructure models http://www.xilinx.com  ISE, EDK, FPGAs, CPLDs, and structured I: IP blocks, C, and RTL; FPGAs http://www.xilinx.com  Xilinx XtremeDSP ASICs RTL; FPGAs http://www.xilinx.com  Hosted Design and Extranet Reuse Services IP delivery systems S: All types of IP reuse.com  Software Configurable Compile a subset of C into Processor hardware for instruction configurable Processors hardware for instruction processors http://www.stretchinc.com  Transaction-based verification C: FPGA-based rapid http://www.prodesign-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Beach     |             | deploy IP in a repeatable,    |                      | http://www.beachsolutions. |

| Altera Quatrus II ASICs RTL; FPGAs http://www.altera.com Platform Xilinx Studio IP integration framework C: IP blocks, FPGAs http://www.xilinx.com http://www.mentor.com/pro ducts/embedded_software/ Graphics Nucleus systems and development tools S: Software nucleus_rtos  Sonics On-chip interconnection I: Bus-functional infrastructure models http: sonicsinc.com  ISE, EDK, FPGAs, CPLDs, and structured I: IP blocks, C, and Xilinx XtremeDSP ASICs RTL; FPGAs http://www.xilinx.com  Hosted  Design and Extranet Reuse Services IP delivery systems S: All types of IP reuse.com  Software Configurable Compile a subset of C into Processor hardware for instruction configurable compiler extensions processors http://www.stretchinc.com Transaction-based verification C: FPGA-based rapid http://www.prodesign-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Solutions | EASI-Studio | reliable manner               | C: Interconnection   | com                        |

| Platform Xilinx Studio IP integration framework C: IP blocks, FPGAs http://www.xilinx.com/http://www.mentor.com/pro/ducts/embedded_software/nucleus_rtos  Sonics Nucleus systems and development tools S: Software nucleus_rtos  Sonics On-chip interconnection I: Bus-functional Sonics Studio infrastructure models http: sonicsinc.com  ISE, EDK, FPGAs, CPLDs, and structured I: IP blocks, C, and Xilinx XtremeDSP ASICs RTL; FPGAs http://www.xilinx.com  Hosted Design and Extranet Reuse Services IP delivery systems S: All types of IP reuse.com  Software Configurable Compile a subset of C into C: Software-processor hardware for instruction configurable Processor hardware for instruction configurable Stretch compiler extensions processors http://www.stretchinc.com http://www.stretchinc.com                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |             | FPGAs, CPLDs, and structured  | I: IP blocks, C, and |                            |

| Xilinx Studio IP integration framework C: IP blocks, FPGAs <a href="http://www.xilinx.com">http://www.xilinx.com</a> Mentor  Family of real time operating Graphics Nucleus systems and development tools S: Software  Sonics On-chip interconnection I: Bus-functional infrastructure models http: sonicsinc.com  ISE, EDK, FPGAs, CPLDs, and structured I: IP blocks, C, and Xilinx XtremeDSP ASICs RTL; FPGAs http://www.xilinx.com  Hosted Design and Extranet Reuse Services IP delivery systems S: All types of IP reuse.com  Software Configurable Compile a subset of C into C: Software- Processor hardware for instruction configurable Stretch compiler extensions processors http://www.stretchinc.com Transaction-based verification C: FPGA-based rapid http://www.prodesign-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Altera    | Quatrus II  | ASICs                         | RTL; FPGAs           | http://www.altera.com      |

| Mentor Graphics Nucleus Sonics Sonics On-chip interconnection ISE, EDK, Hosted Design and Extranet Reuse Sorics Sorics IP delivery systems Sorics Sorics Services IP delivery systems Sorics Sorics Services IP delivery systems Sorics S |           | Platform    |                               |                      |                            |

| Mentor Graphics Nucleus Systems and development tools S: Software  Sonics On-chip interconnection I: Bus-functional  Sonics Studio ISE, EDK, FPGAs, CPLDs, and structured I: IP blocks, C, and RTL; FPGAs Hosted Design and Reuse Services IP delivery systems S: All types of IP Configurable Compile a subset of C into Processor Ardware for instruction  C: FPGA-based rapid  C: FPGA-based rapid    http://www.stretchinc.com                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Xilinx    | Studio      | IP integration framework      | C: IP blocks, FPGAs  | http://www.xilinx.com      |

| Graphics Nucleus systems and development tools S: Software nucleus rtos  Sonics On-chip interconnection I: Bus-functional models http: sonicsinc.com  ISE, EDK, FPGAs, CPLDs, and structured I: IP blocks, C, and XtremeDSP ASICs RTL; FPGAs http://www.xilinx.com  Hosted  Design and Extranet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |             |                               |                      |                            |

| Sonics On-chip interconnection I: Bus-functional models http: sonicsinc.com ISE, EDK, FPGAs, CPLDs, and structured I: IP blocks, C, and Xilinx XtremeDSP ASICs RTL; FPGAs http://www.xilinx.com Hosted Design and Extranet Services IP delivery systems S: All types of IP reuse.com Software Configurable Compile a subset of C into C: Software- Processor hardware for instruction configurable Stretch compiler extensions processors http://www.stretchinc.com Transaction-based verification C: FPGA-based rapid http://www.prodesign-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Mentor    |             | Family of real time operating |                      | ducts/embedded_software/   |

| Sonics Studio infrastructure models <a href="http://www.xilinx.com">http://www.xilinx.com</a> ISE, EDK, FPGAs, CPLDs, and structured I: IP blocks, C, and RTL; FPGAs http://www.xilinx.com  Hosted  Design and Extranet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Graphics  | Nucleus     | •                             | S: Software          | nucleus_rtos               |

| ISE, EDK, FPGAs, CPLDs, and structured I: IP blocks, C, and  Xilinx XtremeDSP ASICs RTL; FPGAs http://www.xilinx.com  Hosted  Design and Extranet Services IP delivery systems S: All types of IP reuse.com  Software Configurable Compile a subset of C into C: Software-Processor hardware for instruction configurable  Stretch compiler extensions processors http://www.stretchinc.com  Transaction-based verification C: FPGA-based rapid http://www.prodesign-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | Sonics      | On-chip interconnection       | I: Bus-functional    |                            |

| Xilinx XtremeDSP ASICs RTL; FPGAs <a href="http://www.xilinx.com">http://www.xilinx.com</a> Hosted  Design and Extranet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Sonics    |             |                               |                      | http: sonicsinc.com        |

| Hosted  Design and Extranet  Reuse Services IP delivery systems S: All types of IP reuse.com  Software  Configurable Compile a subset of C into C: Software- Processor hardware for instruction configurable  Stretch compiler extensions processors http://www.stretchinc.com  Transaction-based verification C: FPGA-based rapid http://www.prodesign-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | •           |                               |                      |                            |

| Design and Extranet Reuse Services IP delivery systems S: All types of IP  Software Configurable Compile a subset of C into Processor hardware for instruction configurable compiler extensions processors http://www.stretchinc.com  Transaction-based verification C: FPGA-based rapid http://www.prodesign-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Xilinx    |             | ASICs                         | RTL; FPGAs           | http://www.xilinx.com      |

| Reuse Services IP delivery systems S: All types of IP reuse.com  Software Configurable Compile a subset of C into C: Software- Processor hardware for instruction configurable Compiler extensions processors http://www.stretchinc.com  Transaction-based verification C: FPGA-based rapid http://www.prodesign-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |             |                               |                      |                            |

| Software Configurable Compile a subset of C into C: Software- Processor hardware for instruction configurable Stretch compiler extensions processors http://www.stretchinc.com Transaction-based verification C: FPGA-based rapid http://www.prodesign-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |             |                               |                      | http://www.design-         |

| Configurable Compile a subset of C into C: Software- Processor hardware for instruction configurable Stretch compiler extensions processors http://www.stretchinc.com  Transaction-based verification C: FPGA-based rapid http://www.prodesign-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reuse     |             | IP delivery systems           | S: All types of IP   | <u>reuse.com</u>           |

| Processor hardware for instruction configurable Stretch compiler extensions processors http://www.stretchinc.com Transaction-based verification C: FPGA-based rapid http://www.prodesign-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |             |                               |                      |                            |

| Stretch compiler extensions processors <a href="http://www.stretchinc.com">http://www.stretchinc.com</a> Transaction-based verification C: FPGA-based rapid <a href="http://www.prodesign-">http://www.prodesign-</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |             |                               |                      |                            |

| Transaction-based verification C: FPGA-based rapid http://www.prodesign-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |             |                               | <u> </u>             |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Stretch   | compiler    |                               |                      |                            |

| ProDesign CHIPit platform prototyping <u>usa.com</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |             |                               | •                    |                            |